#### ΣΧΟΛΗ ΘΕΤΙΚΩΝ ΕΠΙΣΤΗΜΩΝ

# ΔΠΜΣ Space Technologies, Applications and seRvices (STAR) M806 Space Data Systems

Best Practice VHDL Coding for Aerospace Systems

Ακαδημαϊκό Έτος 2023-2024

Νεκτάριος Κρανίτης

### DO-254 and DO-178C Standards

- DO-254 and DO-178C are standards developed by Radio Technical Commission for Aeronautics (RTCA) and adopted by regulatory bodies i.e. the Federal Aviation Administration (FAA) and European Aviation Safety Agency (EASA) for Aerospace industry

- DO-254, "Design Assurance Guidance for Airborne Electronic Hardware (AEH)"

- Provides a structured and standardized approach to the development, verification, and validation of electronic HW used in aerospace systems

- Covers electronic HW components, such as ICs, PCBs, and other electronic equipment, and defines a set of Design Assurance Levels (DALs) that must be met for each component based on level of safety criticality.

- Compliance with DO-254 is required for achieving certification of electronic HW used in airborne systems

- DO-178C, "Software Considerations in Airborne Systems and Equipment Certification"

- Provides a structured and standardized approach to the development, verification, and validation of SW used in airborne systems

- Covers SW components, including OSs, application software, and SW tools, and defines five levels of criticality, called Software Levels (SWLs), that must be met for each component

- Compliance with DO-178C is required for achieving certification of SW used in airborne systems.

- In summary, **DO-254 focuses on electronic HW**, while **DO-178C focuses on SW**, and both standards are critical for ensuring the safety and reliability of airborne systems

### VHDL coding for DO-254 and DO-178C Compliance

- VHDL design with DALA, B and C must establish conformance to VHDL coding standards

- No official list from FAA or EASA

- Guidance & list of rules proposed by DO-254 UG (2010)

- RTCA/DO-254 provides design assurance guidance for airborne electronic HW

- Ensure that AEH works reliably as specified, avoiding faulty operation and potential functional hazards

- Discusses need for "Design Standards"

- FAA Order 8110.105 section 6-2a clarified that HDL coding standards should be defined and checked when it stated:

- "To prevent potentially unsafe attributes of HDLs from leading to unsafe features of the components, we must expect that, if they use an HDL, applicants define the coding standards for this language consistent with the system safety objectives, and establish conformance to those standards by HDL code reviews."

|         |                      | 1 1 1 1                                                                                                                                                                             |

|---------|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DAL     | Failure<br>Condition | Resulting Conditions                                                                                                                                                                |

| Level A | Catastrophic         | Failure may result in deaths and loss of the aircraft                                                                                                                               |

| Level B | Hazardous            | Failure creates a major negative impact on safety or performance or reduces the aircraft crew's ability to operate the aircraft. This can result in serious or fatal injuries.      |

| Level C | Major                | Failure causes significant reduction of the safety margin or significant increase in the aircraft crew workload. Passenger discomfort or minor injuries can result.                 |

| Level D | Minor                | Failure slightly reduces the margin of safety or causes slight increase in aircraft crew workload. Results can include passenger inconvenience or changes to a routine flight plan. |

| Level E | No Effect            | Failure causes no impact or effect on safety, crew workload, or operation of the aircraft.                                                                                          |

## DO-254 UG Positioning Paper

- Provide a list of generally accepted VHDL

design best practice coding guidelines that

should be considered for a fail-safe design,

including DO-254 programs

- These coding guidelines should NOT be viewed as what must be done in a DO- 254 program

- What must be done is always the decision of the applicant in conjunction with the certification authority

- However, if project team is looking for a good foundational set of checks to assess the HDL design quality for their DO-254 program, this document provides that foundation

DO-254 Users Group

Position Paper DO254-UG-001

Best Practice VHDL Coding Standards for DO-254 Programs

COMPLETED 2/26/10 (MODIFIED 9/13/10)

(Rev 1a)

Team Primary Author: Michelle Lange

NOTE: This position paper has been coordinated among representatives from the Europe and US DO-254 users groups. This document is provided for educational and informational purposes only and should be discussed with the appropriate certification authority when considering actual projects. This position paper does not represent an official position the EASA, FAO restrocas/RTCA related committees

## DO-254 UG Positioning Paper

### Following 4 Rule Categories Were Proposed

- Coding Practices [14 Rules CP1 CP14]

- This set of rules ensures that a coding style supporting safety-critical and good digital design practices are used

- Safe Synthesis [21 Rules SS1-SS21]

- This set of rules ensure that a proper netlist is created by the synthesis tool.

- Code Reviews [13 rules DR1 DR13]

- This set of rules are checked to ease design reviews & code comprehension

- Clock Domain Crossings [1 Rule CDC1]

- This rule addresses potential hazards with designs containing multiple clock zones and asynchronous clock zone transitions

- This category ensures that a coding style supporting safety-critical and good digital design practices are used

- Each rule that follows is given a coding practice (CP) number for ease of reference

#### 3. Avoid Hard-Coded Numeric Values (CP3)

For design IP reuse and portability ease, hard-coded numeric values should not be used.

Constants or generics should be used and documented within the design. This will greatly reduce the probability of a design error from creeping into the design code as it is being ported to a new application.

Default severity: Warning

### 4. Avoid Hard-Coded Vector Assignment (CP4)

For vector reset assignments; do not use hard-coded values.

The reset assignment should be done in a way that is independent of the size of the vector. This limits the impact of changing vector sizes and enhances design portability ease.

Default severity: Note

### 5. Ensure Consistent FSM State Encoding Style (CP5)

a. A design should employ a consistent state encoding style for Finite State Machines (FSM).

b.FSM state types should not be hard-coded, unless unavoidable.

Default severity: Error

```

TYPE cpu_sm_state_type IS (

IDLE, -- reset & default state

START OP,

WRITE_DATA,

DO READ,

WAITMEM,

STALL WAIT,

DO RD

-- Note, FSM states are encoded as enumerated type

);

P_CPU_SM_NEXT_STATE : PROCESS( . . . )

BEGIN

CASE current_state_r is

WHEN IDLE =>

WHEN START OP =>

WHEN "0011" => -- Violation, inconsistent state encoding

END CASE;

END PROCESS P CPU SM NEXT STATE;

```

#### 6. Ensure Safe FSM Transitions (CP6)

- a. An FSM should have a defined reset state.

- b. All unused (illegal or undefined) states should transition to a defined state, whereupon this error condition can be processed accordingly.

- c. There should be no unreachable states (i.e., those without any incoming transitions) and dead-end states (i.e., those without any outgoing transitions) in an FSM.

Default severity: Error

Example:

END CASE;

```

TYPE fsm_state_type IS (

IDLE,

-- reset & default state

START_OP,

WRITE_DATA,

DO READ,

WAITMEM,

-- wait for memory response

STALL_WAIT, -- cpu stall

DO RD

-- AIS

-- Commented out AIS state will cause violation

CASE current_state IS

WHEN IDLE

IF (rd_req='1' AND pre='0') THEN

next_state <= DO RD;</pre>

WHEN DO_READ =>

-- Violation, no incoming transition

next_state <= DO_RD;</pre>

WHEN DO_RD

IF (pre='1') THEN

status <= WAITMEM; -- Violation, no outgoing transition

WHEN OTHERS =>

-- Others, including error states

-- transition to the AIS state

next_state <= AIS;</pre>

-- Violation, AIS is not a defined state

```

#### 10. Assign Value Before Using (CP10)

Every object (e.g., signal, variable, port) should be assigned a value before using it.

When objects are used before being defined, a latch may be inferred during synthesis, which is most likely unintentional functional behavior for the design.

Default severity: Warning

```

Example:

ENTITY fifo bk pressure IS

PORT (

-- Port Declarations

clk_ck2 : IN std_logic; -- GLOBAL: downstream clock

rst ck2 n : IN std logic; -- GLOBAL: downstream reset(N)

cntr ck1 i : IN std logic vector(FIFO CNTR-1 DOWNTO 0); -- 9-bit

-- Cut-and-paste error, should be cntr_ck2_i, results in violation

);

ARCHITECTURE rtl OF fifo_bk_pressure is

-- register definitions

signal full_threshold_r : fifo_cntr_type; -- 9-bit data type

threshold proc: PROCESS(cntr_ck2_i, full_threshold_r)

BEGIN

assert bk pressure s <= '0';

ELSIF (cntr_ck2_i = full_threshold_r - CDC_DELAY) THEN

--VIOLATION "cntr_ck2_i" should be assigned before being read

assert_bk_pressure_s <= '1';</pre>

END IF;

END PROCESS threshold_proc;

```

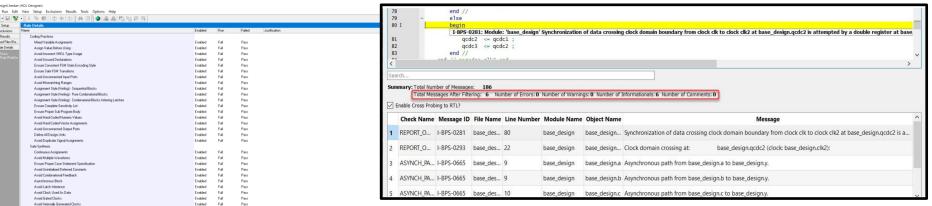

### DO-254 Category: Clock Domain Crossing (CDC)

This set of standards addresses potential hazards with designs containing multiple clock zones and asynchronous clock zone transitions.

### 1. Analyze Multiple Asynchronous Clocks (CDC1)

Any time a design has multiple asynchronous clocks, or if internally-generated clocks are allowed, a thorough clock domain crossing (CDC) analysis should be done.

Improper clock domain crossings result in metastability or indeterminate circuit operation, which can have serious adverse affects on a device's operation. This design guidance needs to be mentioned, even though clock domain crossing issues and analysis is beyond the scope of typical HDL linting tools and beyond the scope of this document.

- The following standards are checked to ensure a proper netlist is created by synthesis tool.

- 1. Avoid Implied Logic (SS1)

Do not allow coding that implies feed-throughs, delay chains, and internal tri-state drivers.

Default severity: Warning

```

Example:

SIGNAL mode : std_logic; -- Internal Tri-state Control

SIGNAL tri bus : std logic vector (1 DOWNTO 0); -- Internal signal

-- (not top level port)

Tristate_Control: PROCESS (mode)

BEGIN

IF (mode = '0') THEN

tri bus <= "OZ"; -- Do not allow internal tristates

ELSE

tri bus <= "ZO"; -- Do not allow internal tristates

END IF;

END PROCESS Tristate_Control;

Example:

ENTITY feed through ea IS

PORT (

a_i : IN std_logic;

av_i : IN std_logic_vector (10 DOWNTO 0);

x_o : OUT std_logic

END feed_through_ea;

ARCHITECTURE rtl OF feed_through_ea IS

BEGIN

x_o <= a_i; -- Violation, feed-through from input port "a_i" to

output port "x_o"

```

### 2. Ensure Proper Case Statement Specification (SS2)

Case statements should:

- a. Be complete

- b. Never have duplicate/overlapping statements

- c. Never have unreachable case items

- d. Always include the "when others" clause

```

CASE addr IS

WHEN "000" =>

clk_div_en <= '1';

WHEN "001" =>

clk_div_en <= '1';

WHEN "000" =>

-- Duplicate/overlapping case specification

clk_div_en <= '1';

-- Incomplete case specification

WHEN "10X" =>

-- Not reachable case specification

xmitdt_en <= '1';</pre>

ser_if_select <= addr(1 DOWNTO 0);

WHEN "110" =>

ser_if_select <= addr(1 DOWNTO 0);

WHEN "111" =>

clr_int_en <= '1';

-- Missing WHEN OTHERS clause

END CASE;

```

### 4. Avoid Latch Inference (SS4)

The HDL coding style should avoid inference of latches.

```

library ieee;

use ieee.std_logic_1164.all;

ENTITY vhdlatch IS

PORT (

in1, in2, in3, in4 : IN std_logic;

out1 : OUT std_logic;

out2 : OUT std logic vector(3 DOWNTO 0));

END;

ARCHITECTURE arch OF vhdlatch IS

BEGIN

PROCESS (in1, in2, in3, in4) -- Violation

BEGIN

IF(in4 = '0') THEN

out2(3) <= in1;

out2(0) <= in2;

ELSE

out2 <= (others => in3);

END IF;

END PROCESS:

END;

```

### 7. Avoid Uninitialized VHDL Deferred Constants (SS7)

Ensure all VHDL deferred constants are initialized.

Default severity: Warning

```

PACKAGE trafficPackage IS

CONSTANT MaxTimerVal: integer

-- Violation. Deferred constant 'MaxTimerVal' without initial

-- value may not be synthesizable

END trafficPackage;

```

#### 8. Avoid Clock Used as Data (SS8)

Clock signals should not be used in a logic path that drives the data input of a register.

Default severity: Error

```

Example:

P_GATED_IN : PROCESS(in1, mclk)

BEGIN

gated in s <= '0';

IF (in1 = TRANSITION) and (mclk = '0') THEN -- Associated Violation

gated in s <= '1';

-- See below

END IF;

END PROCESS P_GATED_IN;

P_PULSE_FF : PROCESS(mclk, rst_n) -- Violation clock used as data

BEGIN

-- Race condition can occur here

IF (rst_n = '0') THEN

pulse r <= '0';</pre>

ELSIF rising edge (mclk) THEN

pulse_r <= gated_in_s;</pre>

END IF;

END PROCESS P_PULSE_FF;

```

### 9. Avoid Shared Clock and Reset Signal (SS9)

The same signal should not be used as both a clock and reset signal.

Default severity: Error

### 10. Avoid Gated Clocks (SS10)

Data signals should not be used in a logic path that drives the clock input of a register.

Default severity: Warning

Clock gating designs for FPGA should not be allowed if the targeted FPGA device does not contain special purpose-built clock gating circuitry in silicon.

### 13. Avoid Mixed Polarity Reset (SS13)

The same reset signal should not be used with mixed styles or polarities.

Default severity: Warning

```

Example:

ARCHITECTURE rtl OF top IS

BEGIN

proc1: PROCESS(clk_master, clk_n, rst_master)

BEGIN

IF rising_edge(clk_master) THEN

IF (rst_master = '1') THEN

-- Violation, inconsistent

q <= '0';

-- reset polarities & style

ELSE

q \ll d1;

END IF;

END IF;

IF (rst_master = '0') THEN

-- Violation, inconsistent

q <= '0';

-- reset polarities & style

ELSIF (falling_edge(clk_n)) THEN

q \ll d2;

END IF;

END PROCESS;

END rtl;

```

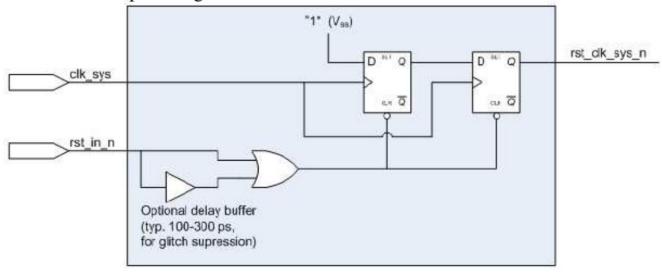

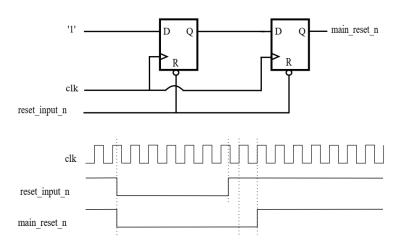

#### 15. Avoid Asynchronous Reset Release (SS15)

Reset signals should have a synchronous release.

For synchronous digital designs, it is considered best practice to generate reset control as asynchronous assertion and synchronous de-assertion signal to avoid problems when the reset signal is de-asserted during the active edge of the clock..

Default severity: Error

#### Example:

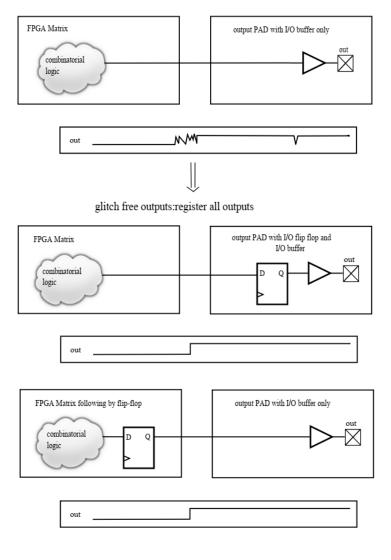

Note that the following figure demonstrates a *correct* on-chip reset scheme as described in the preceding text.

#### 20. Ensure Nesting Limits (SS20)

Conditional branching constructs should have a maximum nesting depth.

Default severity: Warning

```

Example:

```

```

FLIP_FLOP: PROCESS(rst,clk)

BEGIN

IF rst = '1' THEN

qout <= '0';

out_one <= '0';

out_two <= '0';

out_three <= '0';

ELSIF RISING_EDGE(clk) THEN

IF in_one = '1' THEN

out_one <= in_one;

IF in_two = '1'THEN

out_two <= in_two;

IF in_three = '1' THEN -- Violation if set to 3, as 4<sup>th</sup> level

out_three <= in_three;</pre>

```

. .

#### 21. Ensure Consistent Vector Order (SS21)

*Use the same multi-bit vector order consistently throughout the design.*

Default severity: Warning

```

Bus_ascending : IN std_logic_vector (7 DOWNTO 0);

Bus_decending : IN std_logic_vector (0 TO 7); -- Violation if

Descending order enabled

```

### 2. Avoid Mixed Case Naming for Differentiation (DR2)

Names should not be differentiated by case alone.

Default severity: Warning

### Example: ENTITY top IS

```

PORT (nrw: OUT std_logic );

END top;

ARCHITECTURE flow OF top

BEGIN

Nrw <= '0';

-- Violation. Do not allow mixing of case identifier "nrw"

-- Identifiers "nrw" and "Nrw" are differentiated by case only

END

```

### 4. Use Separate Declaration Style (DR4)

Each declaration should be placed on a separate line.

Default severity: Note

```

ARCHITECTURE spec OF status_registers IS

SIGNAL xmitting_r, done_xmitting_r : std_logic; -- declaration

-- Violation. Multiple signals declared in one line,

-- declarations should be on separate lines.

END spec;

```

#### 5. Use Separate Statement Style (DR5)

Each statement should be placed on a separate line.

Default severity: Note

```

Example:

```

```

IF (en_i = '1') THEN

x1_s <= NOT(a1_i); x2_s <= a1_i; -- Violation, multiple statements

ELSE

x1s <= '0'; x2_s <= '0'; -- Violation, multiple statements

END IF;</pre>

```

### 6. Ensure Consistent Indentation (DR6)

Code should be consistently indented.

Default severity: Note

```

FLOP FLIP: PROCESS(rst,clk) -- Consistently formatted

BEGIN

IF rst = '1' THEN

tout one <= '0';

tout two <= '0';

tout three <= '0';

ELSIF rising_edge(clk) THEN

IF in_one = '1' THEN

tout_one <= in_one;

IF in_two = '1' THEN

tout_two <= in_two;

IF in three = '1' THEN

tout_three <= in_three;</pre>

ENDIF;

ENDIF;

ENDIF:

ENDIF;

```

7. Avoid Using Tabs (DR7)

Tabs should not be used.

Default severity: Warning

10. Ensure Consistent File Header (DR10)

Ensure a consistent file header.

Default severity: Warning

11. Ensure Sufficient Comment Density (DR11)

Code should be sufficiently documented via inline comments.

Default severity: Warning

#### 13. Ensure Company Specific Naming Standards (DR13)

Each company or project should establish and enforce its own naming standards.

These standards will vary from company to company, or even project to project, and therefore cannot be explicitly included in a generic set of DO-254 coding standards. However, they should be considered and included in each company's HDL coding standards. The sorts of things to consider include:

- Having the component have the same name as the associated entity

- Ensuring name association between formal and actual generics, ports or parameters

- Enforcing specific filename matching with associated entity

- Enforcing specific object type naming convention, with a prefix or postfix appended to the object name. Choose only one of these two methods (prefix vs. postfix labels) and consistently apply it through out the entire design. Consideration should be give to naming conventions for clocks, resets, signals, constants, variables, registers, FSM State Variables, generics, labels etc. For example:

- a. signals use "\_s"

- b. registers use "\_r"

- c. constants use "\_c"

- d. processes use "\_p"

- e. off-chip inputs use "\_I"

- f. on-chip inputs use "\_i"

- g. off-chip outputs use "\_O"

- h. on-chip outputs use "\_o"

- i. etc.

Default severity: Note

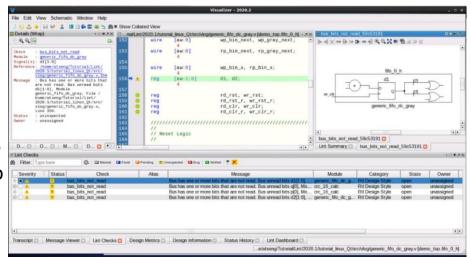

### **Automated Rule Checking**

- Design reviews: can be done manually

- Automated approach (called linting):

- guarantees a more consistent VHDL code quality assessment

- has the added benefit of promoting regular VHDL design checking steps throughout the design development process, as opposed to waiting for gating design reviews where issues can be overwhelming and more costly to address

### **SIEMENS Questa Lint**

BluePearl

### **CNES Rules**

- Originally developed by CNES for internal projects

- To improve the way VHDL code is written and thus reducing the time spent for code review

- Useful for other companies that want to share common VHDL rules between them and their subcontractors

- Handbook is divided into two chapters:

- "Standard Rules": includes general rules or recommendations that are common between all companies working with VHDL. These rules share a general agreement between CNES and partners initially involved. Addition and changes to these rules have to be agreed by everyone.

- "Custom Rules": includes company specific rules that are adapted/refined from standard rules or completely new. These custom rules allow third party companies to create their own version of the VHDL Handbook.

POR VLSI DEVELOPMENT

**CNES Edition**

### **CNES Rules**

Version 2.2 DESIGN AND VHDL HANDBOOK

**Table of Contents**

2.3. Requirement .

STD\_03100 : Dead VHDL code

INTRODUCTION GLOSSARY VERSION HISTORY

| 2021-10-20 |  |

|------------|--|

|            |  |

29

35

#### FOR VLSI DEVELOPMENT

| STANDARD RULES                                           |

|----------------------------------------------------------|

| 1. Formatting                                            |

| 1.1. Naming                                              |

| STD_00100 : VHDL object naming convention                |

| STD 00200 : Name of clock signal                         |

| STD 00300 : Name of reset signal                         |

| STD 00400 : Label for process                            |

| STD_00500 : Name of signal relation with behaviour       |

| STD_00600 : VHDL file extension                          |

| STD_00701 : Preservation of signal name inside an entity |

| STD_00800 : File name convention                         |

| STD_00900 : File name of an entity                       |

| 1.2. FileStructure                                       |

| STD_01000 : Number of entities per file                  |

| STD_01100 : Number of architectures in files             |

| STD_01200 : Number of statements per line                |

| STD_01300 : Number of ports declaration per line         |

| STD_01400 : Instantiation of components                  |

| STD_01500 : Entity ports convention                      |

| STD_01600 : Entity port sort                             |

| STD_01700 : Entity special ports                         |

| STD_01800 : Primitive isolation                          |

| STD_01900 : Indentation of source code                   |

| STD_02000 : Indentation style                            |

| STD_02100 : Compactness of VHDL source code              |

| 2. Traceability                                          |

| 2.1. Versioning                                          |

| STD_02200 : Version control in header of file            |

| STD 02300 : Copyright information in the header of file  |

STD\_02400 : Creation information in the header of the file STD\_02500 : Functional information in the header of file STD\_02600 : IEEE libraries preference ... STD 02700 : Default language . STD 02800 : Comment strategy ... STD 02900 : Comments for entity ports ....

STD\_03000 : Comments for objects declaration and statements

STD\_03800 : Synchronous elements initialization .

STD 04000 : State machine case enumeration completion .

STD 03900 : State machine type definition ...

| c | sigu                                                  | 29 |

|---|-------------------------------------------------------|----|

|   | 3.1. I/O                                              | 29 |

|   | STD_03200 : Unused output ports components management |    |

|   | STD_03300 : Buffer port type                          | 30 |

|   | STD_03400 : Top level ports                           | 31 |

|   | STD_03500 : Record type for top level entity ports    | 32 |

|   | 3.2. Reset                                            | 32 |

|   | STD_03600 : Reset sensitive level                     | 32 |

|   | STD_03700 : Reset assertion and deassertion           | 34 |

|   |                                                       |    |

Table of Contents

| Version 2.2 | DESIGN AND VHDL HANDBOOK<br>FOR VLSI DEVELOPMENT                                               | 2021-10-20 |

|-------------|------------------------------------------------------------------------------------------------|------------|

| 3.          | 4. Clocking                                                                                    | 41         |

|             | STD 04100 : Clock domain crossing                                                              |            |

|             | STD 04200 : Clock domain crossing handshake based                                              | 42         |

|             | STD 04300 : Clock domain crossing FIFOs based                                                  |            |

|             | STD 04400 : Clock management module                                                            | 46         |

|             | STD 04500 : Unsuitability of Clock Reassignment                                                | 47         |

|             | STD 04600 : Clock domain number in the design                                                  | 50         |

|             | STD 04700 : Number of clock domains per modules                                                |            |

|             | STD 04800 : Clock edge sensitivity                                                             |            |

| 3.          | 5. Synchronous                                                                                 |            |

|             | STD 04900 : Edge detection best practice                                                       |            |

|             | STD 05000 : Sensitivity list for synchronous processes                                         |            |

|             | STD 05100 : Metastability management                                                           |            |

|             | STD 05200 : Output signal registration                                                         |            |

| 3           | 6. Combinational                                                                               |            |

| 3.          | STD 05300 : Sensitivity list for combinational processes                                       |            |

|             | STD 05400 : Unsuitability of internal tristate                                                 |            |

|             | STD 05500 : Unsuitability of latches                                                           |            |

|             | STD 05600 : Unsuitability of tatches STD 05600 : Unsuitability of combinational feedbacks      |            |

|             | STD 05700 : Unsuitability of combinational feedbacks STD 05700 : Unsuitability of gated clocks |            |

|             |                                                                                                |            |

| 3.          | 7. Type                                                                                        | 69         |

|             | STD_05800 : Use of VHDL types in RTL design                                                    |            |

|             | STD_05900 : Range for integers                                                                 |            |

|             | STD_06000 : Range direction for arrays                                                         |            |

|             | STD_06100 : Range direction for std_logic_vector                                               |            |

|             | STD_06200 : Management of numeric values                                                       |            |

|             | STD_06300 : Unsuitability of variables in RTL design                                           |            |

| 3.          | 8. Reliability                                                                                 |            |

|             | STD_06400 : Error mitigation strategy                                                          |            |

|             | STD_06500 : Counters end of counting                                                           |            |

|             | STD_06600 : Dimension of comparison elements                                                   |            |

| 3.          | 9. Miscellaneous                                                                               | 78         |

|             | STD 06700 : Unsuitability of wait statement in RTL design                                      | 78         |

|             | STD 06800 : Unsuitability of signal initialization in declaration section                      | 78         |

|             | STD 06900 : Unsuitability of procedures and functions in RTL design                            | 79         |

|             | STD 07000 : Maximum depths of nested objects                                                   | 80         |

| 4. Simu     | lation                                                                                         | 81         |

| 4.          | 1. Miscellaneous                                                                               | 81         |

|             | STD 07100 : Simulation ending                                                                  |            |

|             | STD_07200 : Use of procedures and functions in testbenches                                     | 82         |

|             | STD 07300 : Use of wait statement in testbenches                                               | 83         |

| 5 Impl      | ementation                                                                                     |            |

|             | 1. Analysis                                                                                    |            |

| ٥.          | STD 08000 : Analyze correctness of VHDL                                                        |            |

| CUSTOM DI   | JLES                                                                                           |            |

|             | atting                                                                                         |            |

|             | 1. Naming                                                                                      |            |

| 1.          | CNE 00100 : Identification of active low signal                                                |            |

|             |                                                                                                |            |

|             | CNE_00200 : Unsuitability of frequency in clock name                                           |            |

|             | CNE_00300 : Unsuitability of pin number in signal name                                         |            |

|             | CNE_00400 : Name of testbench entity                                                           |            |

|             | CNE_00500 : Convention for signal naming                                                       |            |

|             | CNE_00600 : Convention for constant naming                                                     |            |

|             | CNE_00700 : Convention for process naming                                                      |            |

|             | CNE_00800 : Convention for generic ports                                                       |            |

|             | CNE_00900 : Convention for custom type naming                                                  |            |

|             | CNE_01000 : Identification of variable name                                                    |            |

|             | CNE_01100 : Identification of ports direction inside entity port name                          | 92         |

| CNE_01300 : Identification of constant name                               | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CNE_01400 : Identification of generic port name                           | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| CNE_01500 : Identification of custom type name                            | . 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| CNE 01700 : Identification of rising edge detection signal                | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CNE 01800 : Identification of falling edge detection signal               | 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CNE 01900 : Identification of registered signals                          | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02000 : Identification of Finite State Machine                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02100 : Name of RTL architectures                                     | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02200 : Name of configuration entity                                  | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02300 : Preservation of clock name                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02400 : Preservation of reset name                                    | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 1.2. FileStructure                                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02500 : Length of entities name                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02600 : Length of signals name                                        | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02700 : Number of lines in file                                       | 10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2. Traceability                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2.1. Versioning                                                           | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02800 : Software VHDL generator in header of file                     | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CNE 02900 : File name in the header of file                               | 11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |